# 晶界层电容器晶界势垒的研究\*

钟吉品 王 鸿 殷之文 (中国科学院上海硅酸盐所)

## 摘 要

以中间夹层的 Schottky 势垒作为晶界层电容器晶界势垒,从理论上分析、推导了电流电压关系 和电容电压关系。利用这些关系式对实验测试数据进行了计算机模拟,并用实验结果和计算机模拟结果检验了该晶界势垒模型的合理性。在此基础上揭示出晶界势垒对晶界层电容器电性能所起的关键作用。

关键词: 半导体陶瓷: 电子陶瓷: 陶瓷电容器: 晶界势垒

## 一、引言

晶界效应与半导体陶瓷的应用密切有关,利用晶界的 Schottky 势 垒模型已解释 了许多 BaTiO<sub>3</sub> 半导体陶瓷的 PTC 效应<sup>[1,2]</sup>和 ZnO 陶瓷的压敏电阻效应<sup>[3-5]</sup>的 实 验 现 象 和问题。七十年代以来又提出了中间夹层的 Schottky 势垒<sup>[6-8]</sup>,对晶界现象更深入地进行了研究。但针对半导体陶瓷晶界层电容器的晶界势垒的研究虽有报导<sup>[9]</sup>但不多。我们在实验中也发现晶界层电容器不仅介电常数高,而且还具有与 ZnO 压敏电阻相同的压敏 特 性。 很可能晶界层电容器的晶界势垒与其它半导体陶瓷有一定的相似之处,为了充分利用晶界层电容器的晶界特点。探明其作用,进行了本工作。

# 二、晶界势垒模型、理论分析与推导

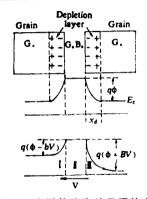

制备晶界层电容器的一个非常重要的工艺是氧化和扩散,使边界形成绝缘层,因此可以认为晶界层电容器的晶界势垒为中间夹层的 Schottky 势垒<sup>[6-8]</sup>,这个中间夹层**就是晶界**的第二相绝缘层。由于大量受主杂质的存在,绝缘层中必然存在很多受主态,在边界处,受主态与 n型半导体晶粒形成一耗尽层,建立起 Schottky 势垒。晶界势垒 模型 如图 1。在这个模型基础上可分析或导出电流电压和电容电压关系。

## 1. 电流电压特性(伏安特性)

当晶界势垒受外加电压作用时被分成三个不同区域如图 1 所示:

- I 区, 受正向电压作用的 Schottky 势垒区:

- Ⅱ区:中间夹层高电阻区:

- Ⅲ区, 受反向电压作用的 Schottky 势垒区。

<sup>\* 1987</sup>年9月1日收到。

图 1 半导体陶瓷的晶界势垒模型 Fig. 1. Barrier model of the grain boundary in semiconductor ceramics

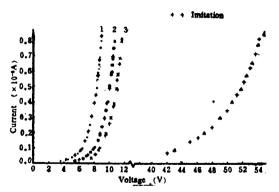

图 2 各种条件氧化的样品的电流电压变 化曲线

Fig. 2. Current-voltage curves of the samples oxidized under various conditions

●800°C for 1h. ×1000°C for 1h. ∘900℃ for 1h. △1200℃ for 1h.

任何时候流经三个区域的电流是相等的,可以用 I 区的电流变化作为整个势垒的伏安特性。 I 区的电流变化关系与 p-n 结的正向电流电压关系相同 $I^{10}$ :

$$I = A'e^{-\phi/KT}(e^{bv/KT} - 1) \tag{1}$$

式中, φ 为势垒高度, b 为外加电压在 I 区上的分配系数。

式(1)可简化为:

$$I = A_1(e^{x_1 v} - 1) \tag{2}$$

对于受反向电压作用的势全区—— II 区,当外加电压增加到某一值时, II 区势全变宽,但上部变窄(如图 1),电子隧道效应将会发生<sup>[7]</sup>,并有较大量的电子流过 II 区。由于电流受到高电阻 II 区的制约,实际情况是 II 区上的电压变化不大。把 II 区上的电压降近似为一个常数,在式(2)基础上可将这种情况下的伏安特性修改为:

$$I = A_2 [e^{K_2(V - V_0 - RI)} - 1]$$

(3)

式中、V。为亚区上的电压降、R 为亚区电阻值、RI 为亚区上的电压降。

## 2. 电容电压关系

在图(1)的耗尽层中,求解泊松方程,可求得耗尽层宽度为[10]。

$$X_{\rm d} = \sqrt{\frac{2 \, \varepsilon}{q N_{\rm D}}} \, (\phi - V)^{1/2} \tag{4}$$

式中, ND 为施主掺杂浓度, q 为电子电荷量。

对于图 1 的势垒模型, 总电容量为:

$$1/C = 1/C_1 + 1/C_{11} + 1/C_{111} = x_{d1}/Q\varepsilon + x_{d111}/Qs + x_{d11}/Q\varepsilon'$$

(5)

式中 $_{1}$ 、 $C_{111}$  和  $_{2}$  分别为受正向和反向电压作用的势垒的容量和介电常数 $_{1}$   $C_{11}$  和  $_{2}$  为中间绝缘层的容量和介电常数**,** $_{2}$  Q 为有效面积因子。

考虑到电压在 I 区和 Ⅲ区上的不同分配,则有:

$$X_{\rm dI} = \sqrt{\frac{2 \varepsilon}{q N_{\rm D}}} (\phi - bV)^{1/2} \tag{6}$$

$$X_{\text{dIII}} = \sqrt{\frac{2 \varepsilon}{q N_{\text{D}}}} (\phi + BV)^{1/2} \tag{7}$$

其中**b** 为 I 区上电压分配系数**B** 为 I 区上电压分配系数。 将(6)式和(7)式代入(5)式得**.**

$$\frac{1}{C} = \frac{1}{Q\varepsilon} \left[ \frac{2\varepsilon}{qN_0} (\phi - bV) \right]^{1/2} + \frac{1}{Q\varepsilon} \left[ \frac{2\varepsilon}{qN_0} (\phi + BV) \right]^{1/2} + \frac{X_{dII}}{Q\varepsilon'}$$

当外电压 V=0 时,

$$\frac{1}{C_n} = \frac{Z}{Q\epsilon} \left( \frac{2 \epsilon}{q N_n} \phi \right)^{1/2} + \frac{X_{dII}}{Q\epsilon'}$$

(8)

$$\therefore \frac{1}{C} = \frac{1}{C_0} + \frac{1}{Q\epsilon} \left( \frac{2\epsilon}{qN_0} \right)^{1/2} [(\phi - bV)^{1/2} + (\phi + BV)^{1/2} - 2\phi^{1/2}]$$

(9)

式(2)、(3)、(9)都是单个晶界的关系式,但把电压分配系数b和B扩充到包含外电压在每个晶界上的分配和每个晶界上的电压在每一个区域上的分配后,式(2)、(3)、(9)对整个陶瓷片就适用了。

## 三、实验与讨论

实验是用作晶界层电容器的  $SrTiO_3$  样品。将掺杂的  $SrTiO_3$  样品以 1420 C4 h 在 空 气中烧结,然后急冷至室温, 使样品半导化<sup>[11]</sup>。 再采取不同的氧化温度进行第二次高温氧化,使晶界重新氧化绝缘,形成晶界势垒。氧化温度分为(1)  $800 C1 h_1$  (2)  $900 C1 h_2$  (3)  $1000 C1 h_1$  (4)  $1200 C1 h_2$

图 2、3 是对这四种氧化温度制得的样片进行测量获得的电流—电压特性(I-V特性)和电容—电压特性(C-V 特性),对图 2 的曲线进行计算机模拟,只有在式(2)中 将 电压 V 修改为( $V-V_0$ ),如式(10)。

$$l = A_1 [e^{x_1(v-v_0)} - 1]$$

(10)

计算机模拟结果才与实际测试结果相吻合(式中V。为一常数)。 计算机模拟结 果 如下:

曲线 1:

$$A_{11} = 1.593 \times 10^{-3}$$

,  $K_{11} = 0.770$ ,  $V_{0_1} = 0.83$ , 误差\*):  $1.40 \times 10^{-5}$   $I = 1.593 \times 10^{-3} [e^{0.770(V-0.83)} - 17]$

曲线 2:

$$A_{12} = 1.420 \times 10^{-8}$$

,  $K_{12} = 0.742$ ,  $V_{02} = 2.05$ , 误差:  $3.49 \times 10^{-6}$   $I = 1.420 \times 10^{-8} (e^{0.742(\nu-2.05)} - 1]$

曲线 3:

$$A_{13} = 1.418 \times 10^{-3}$$

,  $K_{13} = 0.686$ ,  $V_{0_3} = 2.34$ , 误差:  $2.60 \times 10^{-4}$   $I = 1.418 \times 10^{-3} [e^{0.686}(V^{-2.34}) - 1]$

曲线 4:

$$A_{14} = 8.923 \times 10^{-4}$$

,  $K_{14} = 0.201$ ,  $V_{04} = 20.08$ , 误差:  $5.34 \times 10^{-4}$   $I = 8.923 \times 10^{-4} [e^{0.201(V-20.08)} - 1]$

图 2 中的"+"点是计算机模拟的结果与实际吻合的很好。

很明显, $V_0$  表明了外加电压在达到此值之后,Schottky 势垒的导电作用才呈 现出来。另外, $V_0$  也反映了绝缘层的厚度以及绝缘程度,氧化程度越厉害,绝缘层越厚, 绝缘 程度越高, $V_0$  越大。

<sup>\*)</sup> 所有的误差为模拟的结果与每一个测试点的差值的平方和。

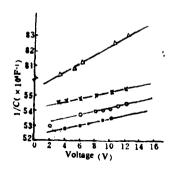

式(8)是推导出的电容一电压关系。如果选择测试电压不太大,电压将分配在每个晶界上,而每一晶界上的电压又将分配在耗尽层上和绝缘层上,那么 BV 和 bV 都将 远 小于 势会高度  $\phi$ ,即, $BV/\phi \ll 1$ , $bV/\phi \ll 1$ 。

图 3 各种条件氧化的样品的电容 电压曲线

Fig. 3. Capacitance-voltage curves of the samples oxidized under various conditions

●800℃ for 1h ○900℃ for 1h ×1000℃ for 1h △1200℃ for 1h

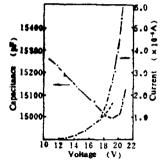

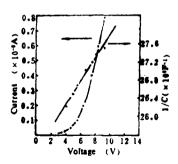

图 5 经 900℃ 1 h 氧化处理样品的伏安特性和电容电压特性曲线

Fig. 5. Current-voltage and capacitancevoltage curves of the sample oxidized at 900°C for 1 h

图 4 由氧化物扩散形成绝缘晶界的样品的电流电压和电容电压曲线

Fig. 4. Current-voltage and capacitance-voltage curves of the sample (the grain boundary barrier of the sample was formed by diffusion of oxides)

图 6 经1000℃ 1 h 氧化处理样 品的伏安特性和电容电压 特性曲线

Fig. 6. Current-voltage and capacitance-voltage curves of the sample oxidized at 1000°C for 1 h

则有:

将一次方以上的项略去得:

$$1/C - 1/C_0 \cong (1/2Q)(1/qN_0 \varepsilon \phi)^{1/2} (B - b)V$$

(13)

可见在测试电压不太大的情况下,1/C 与外加电压 V 呈直线关系,式(13)与图 3 的实际测试结果符合。对于式(13)的斜率部分的讨论是比较复杂的,一方面随着氧化程度的增加,势全高度 Φ 将会有所增大。另一方面,氧化会使绝缘宽度变厚,会使电容的有效面积 Q 因子变小。由于图 3 中电容一电压关系的斜率随氧化程度的不同而异,氧化越厉害,斜率越大。可以认为其有效面积变小起了主要作用。

图 4 是样品在  $H_2/N_2$  还原气氛中烧结、再经扩散  $PbO-Bi_2O_3-B_2O_3-CuO$  四元化合物而得的测试结果,可以看出其电流电压特性和电容电压特性与前面样品测 得 的 结 果是相仿的。

对上面二种样品在较高电压区的伏安特性和电容电压特性测试曲线分别示于图 5 和图 6。可以看出,基本上在使电流增加的趋势增大的电压附近电容发生变化,电容量由下降变为上升,这就是上面讨论的在Ⅲ区发生隧道效应的现象。隧道效应的出现,一方面使电流增加的趋势增大,另方面因穿透Ⅲ区的电子流增大,从而使Ⅲ区的电容量也增大,这就使整个电容量从下降变为上升。电容量上升的规律是很复杂的,准确的关系式尚难找出。式(3)是增大了的电流电压关系式,用图 5、6的数据进行计算机模拟结果为;

图 5

$$A_2 = 7.272 \times 10^{-3}$$

,  $K_2 = 0.828$ ,  $V_0 = 8.23$ ,  $R = 1.314 \times 10^5$ , 误差:  $0.1045$   $I = 7.272 \times 10^{-3} [e^{0.828(V-8.23-1.314 \times 105)}] - 17$

图 6

$$A_2 = 4.508 \times 10^{-3}$$

,  $K_2 = 0.582$ ,  $V_0 = 5.11$ ,  $R = 2.555 \times 10^4$ , 误差: 0.1034  $I = 4.508 \times 10^{-3} [e^{0.582(V-5.11-2.555\times 10^4)} - 1]$

计算机模拟结果与实际测试结果非常吻合,这说明上述理论分析是正确的。在图 5、6 中并未看出击穿现象,由此可知,隧道效应的出现并未使介质击穿,只是使电流增大,只有当外加电压继续增加,中间夹层击穿后,才会发生介质击穿,所以提高中间夹层的耐压是提高晶界层电容器工作电压的关键。

# 四、结论

以中间夹层的 Schottky 势垒作为晶界层电容器的晶界模型, 经理论分析和 推导出的电流电压关系以及电容电压关系与实验测试结果吻合很好。无论是用不同温度氧化还是用氧化物扩散形成的晶界绝缘层都具有同样的关系。电容电压关系和用实验数据进行计算机模拟的电流电压关系表明中间夹层和两个 Schottky 势垒都对电流和电 容 有不同的作用。中间绝缘层对外电压有明显的分压作用。外电压引起的 Schottky 势垒的宽度变化会直接使样品的电容量发生 变 化。 Schottky 势垒的隧道效应会使电流增大、电容量增大,但不影响介质的击穿,介质击穿只有在中间夹层击穿时才会发生, 可 见, 晶界形成的 Schottky 势垒和中间绝缘层的绝缘性对制备大容量、耐高压的晶界层电容器起关键作用。

#### 4 文 数

- [1] Heywang, W.: Solid State Electr., 3 (1) 1961: 51

- [2] Heywang, W.: J. Am. Ceram. Soc., 47(10) 1964: 484

- [3] Levinson L. M. et al.: J. Appl. Phys., 46(3) 1975: 1332

- [4] Levine, J. D.: «CRC Crit. Rev. Solid State Sci.», 5, 1975: 597

- [5] Morris, W. G.: J. Vac. Sci. Technol., 13 (4) 1976: 926

- [6] Hoffmann, B.; Solid State Electronics, 16(5) 1976: 623

- [7] Eda, K.: J. Appl. Phys., 49 (5) 1978: 2964

- [8] Mahan, G. D. et al.: ibid 50 (4) 1979: 2799

- [97 Nobutatsu Yamaoka et al.: Amer. Ceram. Soc. Bull., 62 (6) 1983: 698

- [10] 刘恩科、朱秉升等编。《半导体物理学》。上海科学技术出版社。1984

- [11] 钟吉品、赵梅瑜、王 鸿: 无机材料学报, 2 (1) 1987: 22

# Investigation on the Grain Boundary Barrier of GBBL Capacitors

Zhong Jipin, Wang Hong and Yin Zhiwen (Shanghai Institute of Ceramics, Academia Sinica)

#### Abstract

With the sandwiched Schottky barriers as the grain boundary barriers, the current-voltage relations and the capacitance-voltage relations of the grain boundary barrier layer capacitors (GBBL) have theoretically been analyzed and deducted. By means of those relations, the experimental data have been used for a computerized imitation. The reasonableness of the barrier model was confirmed by comparing the experimental results and the computerized results. It is revealed that the grain boundary barrier plays a quite important role on the electrical properties of GBBL capacitors.

Keywords: Semiconductor ceramics; Electronic ceramics; Ceramics capacitor; Grain boundary barrier